2. Alat dan Bahan [Kembali]

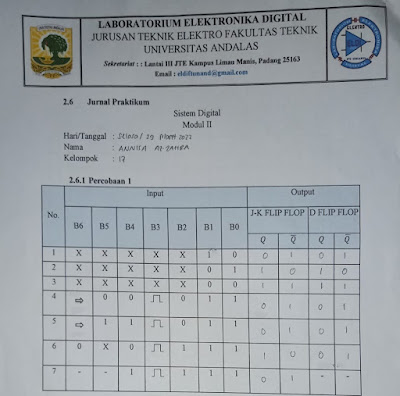

Hubungan input:

B0 = R, B1 = S, B2 = J,

B3 = CLK J flip-flop, B4 = K

B5 = D, B6 = CLK D flip-flop

Rangkaian ini terdiri

dari dua rangkaian flip-flop yang saling terhubung. Input rangkaian divariasikan

kondisinya untuk melihat output serta pengaruh dari perubahan input.

Terdapat 7 kondisi variasi

1. Kondisi

ke-1

B0=0, B1=1, B2=don't care, B3=don't care,

B4=don't care, B5=don't care, dan B6=don't care. Output yang dihasilkan adalah

sama untuk J-K flip-flop dan D flip-flop yaitu Q=0 dan Q’=1

2. Kondisi

ke-2

B0=1, B1=0, B2=don't care, B3=don't care,

B4=don't care, B5=don't care, dan B6=don't care. Output yang dihasilkan adalah

sama untuk J-K flip-flop dan D flip-flop yaitu Q=1 dan Q’=0

3. Kondisi

ke-3

B0=0, B1=0, B2=don't care, B3=don't care,

B4=don't care, B5=don't care, dan B6=don't care. Output yang dihasilkan adalah

sama untuk J-K flip-flop dan D flip-flop yaitu Q=1 dan Q’=1. Kondisi ini

terlarang karena bisa dilihat pada ooutput nilai Q dan Q’ sama.

4. Kondisi

ke-4

B0=1, B1=1, B2=0, B3=clock, B4=0, B5=0, dan

B6=⇨. Output yang dihasilkan

adalah sama untuk J-K flip-flop dan D flip-flop yaitu Q=0 dan Q’=1

5. Kondisi

ke-5

B0=1, B1=1, B2=0, B3= clock, B4=1, B5=1,

dan B6=⇦. Output yang dihasilkan

adalah sama untuk J-K flip-flop dan D flip-flop yaitu Q=0 dan Q’=1

6. Kondisi

ke-6

B0=1, B1=1, B2=1, B3=clock, B4=0, B5=don't

care, dan B6=0. Output yang dihasilkan untuk J-K flip-flop adalah Q=1 dan Q’=0,

sedangkan output yang dihasilkan untuk D flip-flop adalah Q=0 dan Q’=1

7. Kondisi

ke-7

B0=1, B1=1, B2=1, B3=clock, B4=1, B5 dan B6 diputus. Output yang dihasilkan untuk J-K flip-flop adalah Q=0 dan Q’=1. Untuk D flip-flop tidak meghasilkan output karena inputnya diputus.

1. Jelaskan prinsip kerja rangkaian dalam setiap gerbang logika

Bagaimana jika B0 dan B1 sama sama diberi logika 0, apa yang terjadi pada rangkaian? Dengan mengubah B0 sebagai input dari kaki R dan B1 sebagai input dari kaki S menjadi berlogika 0. Maka pin S dan R kedua flip flop akan masuk pada terlarang. Sehingga output dari kedua kaki J-K dan D flip-flop Q berlogika 1 dan Q’ akan berlogika 1. Disebut telarang karena output Q dan Q’ itu sama di mana seharusnya berbeda.

2. Bagaimana jika B3 diputuskan/tidak dibubungkan pada rangkaian apa yang terjadi pada rangkaian?

Jika B3 diputuskan/tidak dihubungkan pada rangkaian, maka untuk D-Flip Flop tidak akan berpengaruh karena tidak ada input yang di putuskan. Sedangkan untuk rangakaian J-KFlip Flop akan sangat berpengaruh pada outputnya, jika tidak ada B3, maka output dari JK-Flip Flop ketika input J atau K diubah tidak akan berubah sesuai kondisinya, karena B3 merupakan input clock dari JK-Flip Flop. Jika tidak ada clock, maka outputnya tidak akan pernah berubah yang mana fungsi clock pada JK flip flop adalah untuk mengendalikan setiap keluaran dari JK flip flop.

3. Jelaskan apa yang dimaksud kondisi toggle, kondisi not change, dan kondisi terlarang pada Flip-Flop!

a. Kondisi Toggle adalah suatu kondisi pada output flip-flop yang merupakan komplemen dari keadaan output sebelumnya.

b. Kondisi Not Change adalah suatu kondisi pada output flip-flop yang tidak mengalami perubahan.

c. Kondisi Terlarang adalah suatu kondisi/keadaan pada flip-flop yang mana ketika masukan pada R dan S sama-sama bernilai 1.

Tidak ada komentar:

Posting Komentar